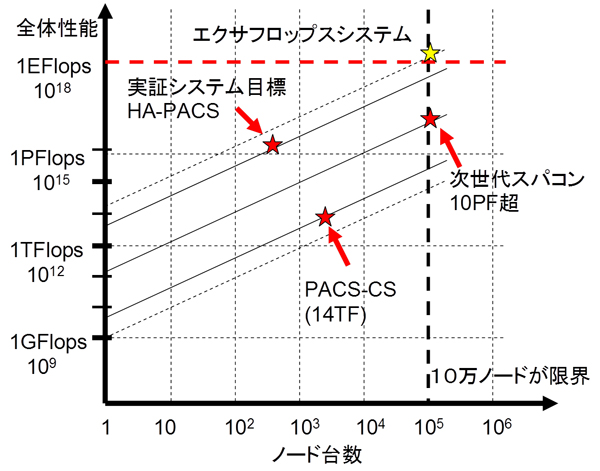

並列型スーパーコンピュータシステムの演算性能は、ノード(プロセッサ)性能×ノード数によって表されます。これまでノード数を増やすことで性能向上を追及してきましたが、電力や故障率などの問題から、その時代が終わりつつあります(weak-scaling問題)。現在のペタスケールを超えてエクサスケールを達成するには、ノード数を10万以上にした場合の耐故障技術を確立することと、ノード単体の演算性能を10TFlopsレベルにする必要があります。後者を達成するためには演算加速機構が有望ですが、これはシミュレーションのステップあたりの時間短縮(strong-scaling問題)を解決することが可能と考えられます。

次世代計算システム開発室では、密結合並列演算加速機構アーキテクチャの研究開発と、密結合並列演算加速機構実証システムHA-PACSの構築を行うことで、1ペタフロップス規模のシステムを開発し、エクサフロップスに向けた実証実験を行います。

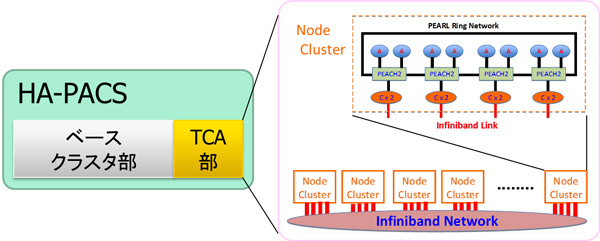

密結合並列演算加速機構実証システムHA-PACSは、ベースクラスタ部分と、演算加速機構を「密結合並列演算加速機構(TCA:Tightly Coupled Accelerators)」で強化した部分からなります。

性能目標:ベースクラスタ部が268ノード×3 TFlops(GPU 2660 GFlops+CPU 332.8 GFlops)=802 TFlops、TCA部で200 TFlops以上。合わせて1 PFlops以上。

ベースクラスタ部

GPGPU(GPU)は、本来グラフィック処理に用いられていたプロセッサを、科学技術計算の加速機構として利用したものです。近年、半導体の急速な進歩にともない多くの演算器を搭載し、大幅な性能向上をしています。HA-PACSプロジェクトでは、演算加速機構としてGPUおよびGRAPE-DR(国立天文台で開発)を検討します。

密結合並列演算加速機構HA-PACS/TCA

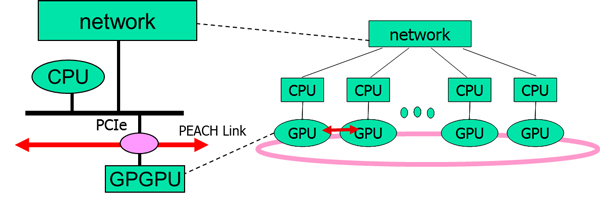

現在の重要なボトルネックになっている、演算加速機構間の通信を直結することによって、通信性能の改善を図り、これまで通信がネックとなって適用できなかったアプリケーションの開拓、これまでのアプリケーションの加速を図ります。

PEARL

PCIeを直結するPEARL(PCI-Express Adaptive and Reliable Link)を開発し、加速機構を直結することによって、通信の遅延の低減、バンド幅の増強を図ります。そのためのチップPEACH2(PCI-Express Adaptive Communication Hub 2)とボードを開発します。PEACH2は、ハードウエアを書き換えることのできるFPGA(Field Programmable Gate Array)を用いて設計します。

PEARLが機能することで、以下の利点を生み出すことができます。

・GPU間の自律通信が可能→汎用コードと加速コードの高性能並列実行

・GPUメモリ間コピーをダイレクトに実行可能→GPUのみによる高速並列処理

・GPUメモリ上のデータのダイレクトI/O→耐故障実行時のオーバヘッド削減等

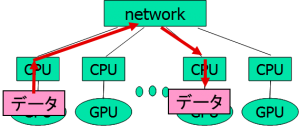

PEARLがない場合は、以下の問題が起こります。

・GPU間結合/通信はCPUが制御→CPU制御に依存、効率低下(例:CPUが入出力制御を行っている間のGPU通信など)

・GPUメモリ間のコピーは最大3ステップをかけて実行→並列処理効率大幅減(データ転送ピーク性能が1/3に低下)

・GPUメモリ上のデータのHDDなどへのI/O処理もCPU経由